**Research Article**

### European Journal of Technique

journal homepage: https://dergipark.org.tr/en/pub/ejt

Vol.13, No.2, 2023

# Design and Testing of a Wireless Communication Enabled FPGA Development Board: A Comprehensive Education and Application Platform from IoT to Circuit Design

### Nebi Karagedik<sup>1</sup>, Sezen Bal<sup>2</sup> and Ayşe Yayla <sup>3\*</sup>

<sup>1</sup>TELFIX, Istanbul, Turkey. (e-mail: n.karagedik@hotmail.com). <sup>2</sup>Marmara University, Vocational School of Technical Sciences, Department of Computer Technologies Kartal, İstanbul, Turkey. (e-mail: sezen.bal@ marmara.edu.tr).

<sup>3\*</sup>Marmara University, Vocational School of Technical Sciences, Department of Electronics and Automation, Kartal, İstanbul, Turkey. (e-mail: acetinkaya@marmara.edu.tr).

#### **ARTICLE INFO**

Received: Dec., 03. 2023 Revised: Dec., 27. 2023 Accepted: Dec, 27. 2023

Keywords: FPGA Circuit Design Digital Design Lecture VHDL IoT Corresponding author: Ayse YAYLA

ISSN: 2536-5010 / e-ISSN: 2536-5134

DOI: https://doi.org/10.36222/ejt.1399107

#### ABSTRACT

Field Programmable Gate Array (FPGA) is an integrated circuit (IC) that can be reprogrammed or configured by the customer or designer after production for rapid prototyping and post-process development. In this study, a cost-effective FPGA development board is designed to create basic engineering education applications and implement them in real-time. The Printed Circuit Board (PCB) design of the FPGA development board layout was precisely crafted using EasyEDA software to ensure robust and reliable connectivity between the FPGA and its peripherals. The FPGA development board utilizes an Altera Cyclone IV E-series chip and includes Bluetooth and Wi-Fi modules to provide a wider range of applications. This integration simplifies the use of wireless communication in various projects and applications for researchers and engineers. To verify the accuracy of the proposed board, simulations of selected digital designs and Bluetooth applications were first performed in VHDL (Very High Speed Integrated Circuit Hardware Description Language) using Intel® Quartus® Prime Lite Edition software. Then, experiments were performed on the board following the pin assignment configurations. It was observed that the developed applications worked successfully on the FPGA development board. As a result, this board, equipped with Bluetooth and Wi-Fi modules, offers a fast and cost-effective solution for users in various fields such as mobile, robotics, smart home systems, and remote monitoring and control devices.

#### 1. INTRODUCTION

Digital Logic Design course has an important position in the curriculum for both computer engineering and the electrical engineering departments [1]. The objective of this course is to provide students to get their exposure to the hardware design by learning the basic concepts of digital design and performing their corresponding experiments. It is very important that the content of the digital design course reflects the current design styles used in the industry. For this reason, FPGA (Field Programmable Gate Array) technology has been incorporated into the experimental education of digital logic design course in order to train expert engineers to adapt to the development trend of digital electronic technology that the industry requires.

FPGAs are programmable, reconfigurable semiconductor devices developed for the purpose of implementing and testing the digital circuits required by the designer [2-4].

FPGAs are generally used to create prototypes of newly designed ASIC circuits or to test the physical implementation of an algorithm. Today, FPGAs are used in a wide range of areas, especially in the military and defense industry [5], communications [6], audio [7] and image processing [8], automotive [9,10] and consumer electronics [11,12].

When developing FPGA-based applications, usually existing development boards are preferred. Procuring these development boards from abroad and their high costs create difficulties in accessing development boards for researchers who want to improve and progress in this field. For this reason, in this study, a low-cost FPGA development board has been designed that can be easily accessed by students studying in universities, especially engineering faculties and vocational schools, academicians who want to develop applications, and anyone interested in hardware design as a hobby. Thus, with this developed board, students studying in relevant departments of universities will be able to access this development board in a cost-effective manner and thus, students who are more equipped on FPGA can be trained. By adding Bluetooth and Wi-Fi modules that are not included in the Altera DE2 board, which is closest to it in the market, a wider range of application development areas have been created in this designed board.

The study is organized as follows: Related works about applications developed using the FPGA board are described in the second section, and the development of the FPGA development board is described in the third section. The VHDL software of the applications implemented using the FPGA development board and the processes regarding the results obtained as a result of assignment to the board are explained in the fourth section. In the fifth and last chapter, the cost study of the developed board was conducted and the results were interpreted.

#### 2. RELATED WORKS

This chapter deals with FPGA technology under two separate subheadings. The first part presents the applications performed with the existing FPGA boards available in the market and produced by various companies. The second part presents new FPGA boards specially designed and developed by researchers for specific needs and the applications performed with these boards.

## 2.1. Studies Performed Using FPGA Development Board

Saif and et all. designed and implemented an educational processor based on RISC-V architecture on FPGA. Additionally, an assembler was designed and developed that can translate assembly code into RISC-V standard machine codes that can help the users to operate the CPU easily [13].

Surekha and et all described the VLSI (Very Large Scale Integration) design of an Arithmetic Logic Unit (ALU). The design has been simulated and tested by using Xilinx ISE design suite 14.7 that is a prominent tool in FPGA development. The proposed ALU design is generated a delay of 125.711 ns [14].

Panigrahi and et all. designed a 4-bit ALU using Xilinx VIVADO 2016.2 and analyze the design parameters on FPGA by using VERILOG. They simulated and synthesized the various parameters such as speed improvement, less power consumption and better utilization of ALU to measure the efficiency of an algorithm [15].

Sağlam and Kaçar designed a 64-bit ALU by using the VHDL and Altera FPGA families, synthesized and simulated with the help of Altera Quartus II and Modelsim-Altera v10.1d software. The proposed design allows the processing of the signed numbers and also Conditional Sum Adder (COSA) is used in addition operation instead of Carry Ripple Adder (CRA) or Carry Look-ahead Adder (CLA). The output of the addition operation was obtained in a shorter time that the adder with COSA is approximately 6 times faster than adder with CRA [16].

Karakaya and et all. introduced a systematic methodology for implementing digital piecewise linear (PWL) functions within nonlinear dynamical systems, enabling the representation of complete behaviors within a single model. The proposed design takes the number of scrolls as input and efficiently generates chaotic PWL signals using a reduced number of FPGA resources. The implementation stage of the study realized by using Xilinx Kintex-7 KC705 Evaluation Board [17].

# 2.2. Studies Designing and Developing FPGA Development Board

Keskin and Koyuncu designed an FPGA-based development board in their study. The development board was developed by selecting the FPGA chip of the XC2C64A-7-VQ44 family from Xilinx, and half adder and up counter applications were implemented as sample applications [18].

Zhao and et all designed a pocket development board that consists of two parts: the core circuit and the peripheral circuit. The core circuits include Altera company Cyclone IV series EP4 CE10 f-17 type FPGA chip, as the core of the hardware circuit of the control unit. Also the hardware circuit of the development board consists of the peripheral circuits that are LED lights, 6 seven-segment digital tubes, buttons and buzzers. These peripheral circuits can carry out independent experiments, and they can be combined with each other [19].

Gao developed Altera EPM7164S chip based FPGA Experiment and Development Board that has high on-board resource utilization, expandable, easy self-design and reasonable cost to overcome the shortcomings of fixed connections, large and fully functional of FPGA experimental box. FPGA Experiment and Development Board can use Quartus II integrated development environment to complete the design. It is suitable for VHDL hardware language and Verilog hardware language [20].

#### 3. DESIGN PROCESS OF FPGA DEVELOPMENT BOARD

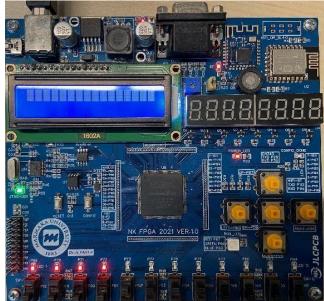

In this study, an FPGA development board was designed to execute fundamental digital logic design applications as well as Bluetooth and Wi-Fi applications. EP4CE6E22C8N chip from the Altera Cyclone IV family was used as the FPGA chip in the design of the development board.

In the development of the FPGA board, first the connections of the FPGA chip with the peripherals were determined and the necessary PCB drawings were made using the EasyEDA program.

The features of the developed FPGA board can be listed as follows: EP4CE10E22C8N was used as the FPGA chip. There is an integrated JTAG interface for programming and debugging FPGA chip, 50MHZ crystal, 5 button inputs and AT24C04 Serial EEPROM for I2C serial communication protocol on the board. With the USB-TTL serial port on the board, it will be possible to communicate with external hardware units such as PCs and embedded systems in accordance with RS232 standards.

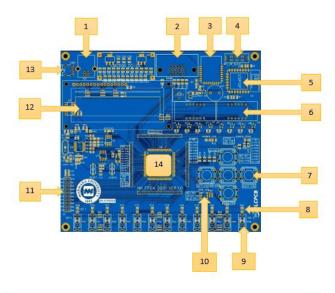

The board also includes 1 X 12 slide switches to obtain input at logic 0 and logic 1 levels in the experiments, 12-bit LEDs, 8 pieces of 7 segment displays with common anode coded 3461BS (4x2 indicator block) and a buzzer. There is also a 1602 character-type LCD (Liquid Crystal Display) interface, VGA display port for visual applications, Input/ Output Pins, a Bluetooth and Wi-Fi modules communicating with UART protocol on the board. The FPGA development board PCB layout and feature callout is shown in Fig. 1.

| Callout | Component Description           | Callout | Component Description  |

|---------|---------------------------------|---------|------------------------|

| 1       | USB Type B                      | 8       | 12 X LEDs              |

| 2       | VGA Connector                   | 9       | 12 X slide switches    |

| 3       | Wi-Fi Module                    | 10      | RGB Led                |

| 4       | Select jumper (Wi-Fi/Bluetooth) | 11      | GPIO Pins              |

| 5       | Bluetooth Module                | 12      | LCD Display            |

| 6       | 8 digit 7 Segment display       | 13      | UART/JTAG USB Port     |

| 7       | 5 X push buttons                | 14      | Altera Cyclone IV FPGA |

|         |                                 |         |                        |

Figure 1. FPGA board PCB layout design and feature callout

#### 4. SAMPLE APPLICATIONS REALIZED ON DEVELOPMENT BOARD

Altera Intel® Quartus® Prime Lite Edition design software was used for testing this FPGA-based development board and coded using the VHDL language. 4-bit Arithmetic Logic Unit (ALU) design, 3- bit Down Counter design and Bluetooth application were realized on this board.

#### 4.1. ALU Design

ALU is the main component of the central processing unit in the computer system, which means arithmetic logic unit and performs arithmetic and logic operations [14]. ALU mainly handles arithmetic operations such as addition, subtraction, division, multiplication, and logical operations such as "AND", "OR", "EXCLUSIVE OR (XOR)", etc., and performs scrollrotation operations [15].

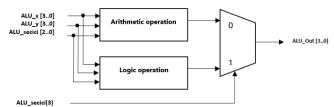

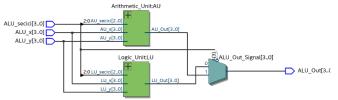

In this study, a 4-bit ALU design, the diagram of which is shown in Fig. 2, was realized by using the switches and LEDs on the designed FPGA development board.

Figure 2. ALU Design Diagram

In this application, which is carried out using the VHDL hardware description language, the x and y inputs given as N bits, are set to 4 bits. The first 3 bits of the selective inputs,

which is determined as 4 bits, are used to select arithmetic and logical operations, and the 4th bit determines which operation result will be transferred to the output in the MUX circuit. The table of arithmetic and logic operations that can be performed with this ALU design is given in Table I.

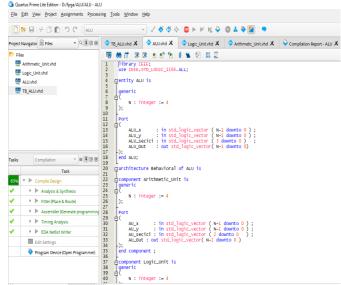

In this application, which was carried out using VHDL structural style, the necessary VHDL code files were first created to perform arithmetic and logical operations. Then, a main file called ALU was created to interconnect the components (arithmetic and logic) within an architecture. The VHDL code of the ALU main file is shown in Fig. 3.

|                                 | TABLE I   |                                      |  |  |  |  |

|---------------------------------|-----------|--------------------------------------|--|--|--|--|

| ALU OPERATIONS AND SELECT LINES |           |                                      |  |  |  |  |

| Operation                       | Selective | Function                             |  |  |  |  |

|                                 | inputs    |                                      |  |  |  |  |

|                                 | 0000      | transfer the x value to the output   |  |  |  |  |

|                                 | 0001      | x value increased by 1               |  |  |  |  |

|                                 | 0010      | x value decreased by 1               |  |  |  |  |

| Arithmetic                      | 0011      | transfer the y value to the output   |  |  |  |  |

| operation                       | 0100      | y value increased by 1               |  |  |  |  |

|                                 | 0101      | y value decreased by 1               |  |  |  |  |

|                                 | 0110      | add the value of x to the value of y |  |  |  |  |

|                                 | 0111      | subtract the value of y from the     |  |  |  |  |

|                                 |           | value of x                           |  |  |  |  |

|                                 | 1000      | NOT x                                |  |  |  |  |

|                                 | 1001      | NOT y                                |  |  |  |  |

|                                 | 1010      | AND (x and y)                        |  |  |  |  |

| Logical                         | 1011      | OR (x or y)                          |  |  |  |  |

| operation                       | 1100      | NAND (Not AND)                       |  |  |  |  |

|                                 | 1101      | NOR (Not OR)                         |  |  |  |  |

|                                 | 1110      | XOR (Exclusive OR)                   |  |  |  |  |

|                                 | 1111      | XNOR (Exclusive NOR)                 |  |  |  |  |

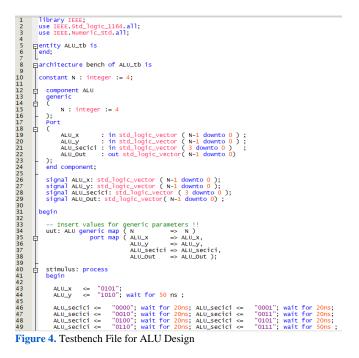

Before testing the created ALU application on the FPGA development board, it is necessary to test whether the codes work correctly or not as a simulation. MODELSIM program was used for this. For this process, first a test file was created. The testbench file of the ALU design is shown in Fig. 4.

Figure 3. ALU Design VHDL File

#### EUROPEAN JOURNAL OF TECHNIQUE, Vol.13, No.2, 2023

RTL (Register Transfer Level) diagram visually illustrates how a design written in a hardware description language will be converted into gate-level logic during the logic synthesis process. This visualization allows the designer to evaluate the behavior and performance of the design and make improvements where necessary. The RTL diagram of the ALU design is shown in Fig 5.

Figure 5. RTL Schema for ALU Design

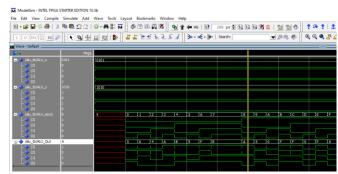

In the test file, x input value was selected as "0101 (Decimal 5)" and y input value was selected as "1010 (Decimal 10-Hexadecimal A)". The first 8 states of the 4-bit selective bit are used to select arithmetic operations and the last 8 states are used to select logic operations. The result screen obtained by running this simulation, in which all arithmetic and logic operations are tested, is shown in Fig. 6.

Figure 6. MODELSIM Simulation Result for ALU Design

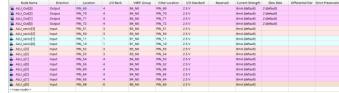

In the next stage, the pin assignments of the FPGA chip are carried out so that the code tested to work correctly as a result of the simulation can be tested by placing it on the FPGA development board. The first 4 keys of the 12 keys of the FPGA board are designated for the selector bits, the next 4 keys are determined for the x value, and the last 4 keys are determined for the y value. In order to observe the results, 4 LEDs were selected as seen in Fig. 7.

Figure 7. Pin Assignment for ALU Design

After the pin assignment is completed, the FPGA development board is programmed. Images of the ALU application performed on the designed FPGA development board are presented in Fig. 8 and Fig. 9, respectively.

Figure 8. Selection Bits 0000 and s<= x (x =1111)

Figure 9. Selection Bits 0011 and s<= y (y =0011)

#### EUROPEAN JOURNAL OF TECHNIQUE, Vol.13, No.2, 2023

#### 4.2. 3- bit Down Counter (Schematic Application)

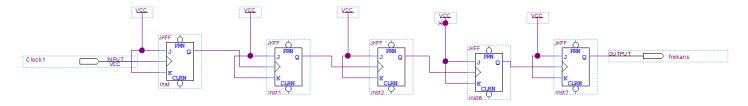

3-bit down counter circuit has been designed as a schematic application in the Quartus® Prime Lite Edition design software, where both schematic and code design is possible. Since the designed FPGA development board has a 50 MHz crystal oscillator, changes that will occur in a counter application using this internal clock pulse may not be discernible by the human eye. For this reason, in the design of this application, a schematic design for a five-bit frequency divider using J-K Flip Flop which is the one-bit memory element was initially designed to reduce the internal clock pulse as seen in Fig. 10.

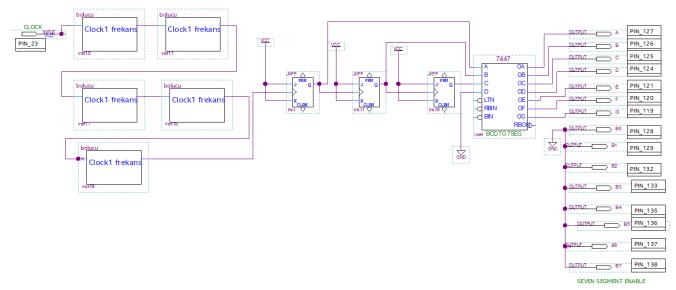

This frequency divider schematic file saved as symbol to be used in the 3-bit down counter circuit. The down counter designed by using J-K FF and 7447 BCD to Seven Segment Decoder was used to transfer the counter values to the seven segment display as seen in Fig. 11.

In this application designed with positive-edge triggering, after creating BDF files, the developed study was tested in a simulation environment to verify its correct functionality. In this study simulated using the University Program VWF, the necessary signals for driving the seven-segment display are illustrated in Fig. 12.

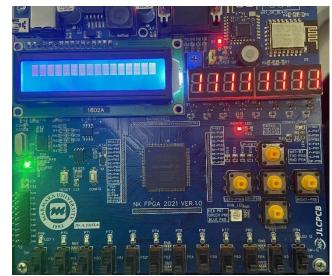

After the successful completion of the testing process in the simulation environment, the necessary pin assignments for the seven-segment display have been implemented, and the counting process has occurred as depicted in Fig. 13.

#### 4.3. Bluetooth Application

In the board design, a Bluetooth module is placed on the development board to enable easy communication between mobile applications and the FPGA. This module communicates with the FPGA chip via Universal Asynchronous Receiver Transmitter (UART) communication protocol. The oscillator on the development board operates at 50 MHz Bluetooth supports UART protocol communication utilizing a range of baud rates, from 1200 to 115200 baud and in this application, the baud rate was chosen 115200 baud. In the VHDL code, a generic is used to determine how many clock cycles there are in each bit by using the code: (Main Frequency) / (UART Baud Rate). The VHDL implementation of UART receiver is shown in Fig. 14.

Figure 10. Frequency Divider (f clock /5) bdf file

Figure 11. 3-bit down counter bdf file

Copyright © European Journal of Technique (EJT)

#### EUROPEAN JOURNAL OF TECHNIQUE, Vol.13, No.2, 2023

|          | Name  | Value at<br>0 ps | 0 ps<br>0 ps | 20.0 ns | 40.0 ns | 60.0 ns | 80.0 ns | 100 <sub>,</sub> 0 ns | 120 <sub>,</sub> 0 ns | 140 <sub>,</sub> 0 ns |   |

|----------|-------|------------------|--------------|---------|---------|---------|---------|-----------------------|-----------------------|-----------------------|---|

| -        | clock | в 0              | <u> </u>     |         |         |         |         |                       |                       |                       | ſ |

| <u>.</u> | А     | BO               |              |         |         |         |         | 1                     |                       |                       | L |

| ut       | в     | BO               |              |         |         |         |         |                       |                       |                       | l |

| ut       | с     | во               |              |         |         |         |         |                       |                       |                       | ļ |

| <u>.</u> | D     | BO               |              |         | 1       |         |         | 1                     |                       |                       | L |

| ut       | Е     | BO               |              |         | 1       |         |         |                       |                       |                       | L |

| eut      | F     | в 0              |              |         | 1       |         |         |                       |                       |                       | L |

| eut      | G     | B1               | 1            |         | 1       |         |         |                       |                       |                       | Ì |

Figure 12. 3-bit down counter wave chart

Figure 13. 3-bit down counter 7 Segment Display Result

In this study, an application was developed to display the binary equivalent of the data in the ASCII table on LEDs that we send from devices (tablet or phone) running on the Android operating system. Additionally, in this application, the RGB LED on the development board is set to light up in different colors for a few values. For example, when the value 1 is sent, it turns red, when the value 2 is sent, it turns blue, and when the value 3 is sent, it turns green. When a value outside of these specified values is encountered, the LED displays white, which is a combination of the three primary colors at equal intensities. In Fig. 15, the screenshot of the application is shown for the value G.

| library ieee;                                                                     |        |

|-----------------------------------------------------------------------------------|--------|

| use ieee.std logic 1164.ALL;                                                      |        |

| use ieee.numeric std.all;                                                         |        |

| entity UART RX is                                                                 |        |

| generic (                                                                         |        |

| CLKS PER BIT : integer := 434 50.000.000/115200=434 Baudrate icin                 |        |

|                                                                                   |        |

| port (                                                                            |        |

| rst : in std logic;reset pin 25                                                   |        |

| i Clk : in std logic; clock giris 50 MHZ pin 23                                   |        |

| i RX Serial : in std logic; Uart rX data pin 114                                  |        |

| o RX DV : out std logic; uart data gecerli pin 28 led                             |        |

| o RX Byte : out std logic vector (7 downto 0);                                    |        |

| r LED Pin1 : out std logic; pin 66 green                                          |        |

| r LED Pin2 : out std logic;pin 67 red                                             |        |

| anode : out STD LOGIC VECTOR (7 downto 0);                                        |        |

| cathodes : out STD LOGIC VECTOR (7 downto 0)                                      |        |

| );                                                                                |        |

| end UART RX;                                                                      |        |

| architecture rtl of UART RX is                                                    |        |

| type t SM Main is (s Idle, s RX Start Bit, s RX Data Bits,s RX Stop Bit, s C      | leanup |

| <pre>signal r SM Main : t SM Main := s Idle;</pre>                                |        |

| signal r RX Data R : std logic := '0';                                            |        |

| signal r RX Data : std logic := '0';                                              |        |

| <pre>signal r Clk Count : integer range 0 to CLKS PER BIT-1 := 0;</pre>           |        |

| signal r Bit Index : integer range 0 to 7 := 0; Toplam 8 bit                      |        |

| <pre>signal r RX Byte : std logic vector(7 downto 0) := (others =&gt; '0');</pre> |        |

| signal r RX DV : std logic := '0';                                                |        |

| begin                                                                             |        |

| p SAMPLE : process (i Clk)                                                        |        |

| begin                                                                             |        |

| if rising edge (i Clk) then                                                       |        |

| r RX Data R <= i RX Serial;                                                       |        |

| r_RX_Data <= r_RX_Data_R;                                                         |        |

| end if;                                                                           |        |

| end process p_SAMPLE;                                                             |        |

Figure 14. VHDL file for UART application

Figure 15. Bluetooth Application Result for the value "G"

#### 5. DISCUSSIONS AND RESULTS

Without the need for additional wireless components, users may quickly and affordably develop and test design solutions for IoT applications with the help of the suggested FPGA evaluation board. Table II contains the table that displays the cost of this board. Additionally, this FPGA development board is approximately 50% below the price of other boards available on the market [21].

The integration of an FPGA development board with internal modules for Bluetooth and Wi-Fi can prove to be especially helpful in fields like defense, aerospace, automotive, medical devices, and smart city infrastructure that demand high-performance hardware solutions and wireless communication. Since internal modules are usually pre-tested and integrated, their usage may be simple. In difficult environments, wireless communication is very beneficial.

| COMPONENT PRI                                                      | TABLE    |     |                    |

|--------------------------------------------------------------------|----------|-----|--------------------|

| Component                                                          | Quantity |     | <b>Total Price</b> |

| Altera Cyclone IV<br>EP4CE6E22C8N                                  | 1        | 16  | 16                 |

| PIC16F45                                                           | 1        | 0.8 | 0.8                |

| LCD                                                                | 1        | 0.8 | 0.8                |

| Bluetooth Module                                                   | 1        | 0.6 | 0.6                |

| ESP 12F Wi-Fi                                                      | 1        | 0.8 | 0.8                |

| Module                                                             |          |     |                    |

| 7 Segment Display                                                  | 2        | 0.2 | 0.4                |

| Switches                                                           | 12       | 1   | 12                 |

| Power Module                                                       | 1        | 0.5 | 0.5                |

| VGA Socket                                                         | 1        | 0.2 | 0.2                |

| SPI Flash and<br>EEPROM                                            | 1        | 1   | 1                  |

| Other Materials<br>(Led, resistor,<br>buzzer, transistor,<br>etc.) | 1        | 2   | 2                  |

| PCB                                                                | 1        | 2   | 2                  |

|                                                                    | Total    |     | 37.1               |

#### 6. CONCLUSION

In this study, FPGA development board with the necessary hardware components has been designed in order to implement the real-time implementation of fundamental digital applications and designs in the field of engineering. EasyEDA program has been used to design the PCB for the FPGA development board. The development board is equipped with Bluetooth and Wi-Fi modules to offer a wider range of application development areas such as mobile, robotics, smart home systems, and remote monitoring and control devices. FPGA development board has been tested using Intel® Quartus® Prime Lite Edition software for sample digital design and Bluetooth applications that have been coded in VHDL language. Testing of sample digital system design projects was initially carried out in a simulation environment.

After the successful execution of simulation tests, the necessary pin assignments for inputs and outputs have been done, and subsequently, FPGA chip has been programmed via JTAG interface. As a result, it was observed that sample digital system design projects and the Bluetooth project worked successfully on the FPGA development board.

With the FPGA development board presented in this study, a cost-effective FPGA development board that can be used in basic engineering education fundamental applications as an alternative to the FPGA development boards procured from abroad at high expenses has been successfully implemented.

#### REFERENCES

- S. Azimi and S. Abba Ali, "FPGA programming with VHDL: A laboratory for the students in the Switching Theory and Digital Design course," Bachelor's Thesis in Computer Science and Engineering, 2023.

- [2] İ. Savran, "Donanım Tanımlama Dili VHDL ve FPGA Uygulamaları," İstanbul: PapatyaBilim, 2017.

- [3] S. Denholm, "Improving low latency applications for reconfigurable devices," PhD Thesis, Department of Computing, Imperial College, London, United Kingdom, 2023.

- [4] B. Grady and J. H. Anderson, "Synthesizable heterogeneous FPGA fabrics," in 2018 International Conference on Field-Programmable Technology (FPT), 2018: IEEE, pp. 222-229.

- [5] N. Pillutla and S. Kumar, "FPGA Implementation of Multi-RT Protocol for Avionics Simulation" IEEE International Systems Conference (SysCon) pp. 1-4, 2023.

- [6] S. Ricci, S. Caputo, and L. Mucchi, "FPGA-Based Pulse Compressor for Ultra Low Latency Visible Light Communications," Electronics, vol. 12, no. 2, p. 364, 2023.

- [7] M. A. A. Al-Dulaimi, H. A. Wahhab, and A. A. Amer, "Design and Implementation of Communication Digital FIR Filter for Audio Signals on the FPGA Platform," Journal of Communications, vol. 18, no. 2, 2023

- [8] S. S. Antora, Y. K. Chang, T. Nguyen-Quang, and B. Heung, "Development and Assessment of a Field-Programmable Gate Array (FPGA)-Based Image Processing (FIP) System for Agricultural Field Monitoring Applications," AgriEngineering, vol. 5, no. 2, pp. 886-904, 2023.

- [9] P. Chen, Y. Chen, and T. Shi, "Real-time simulation and research of motor controller based on FPGA," in Third International Conference on Mechanical Design and Simulation (MDS 2023), 2023, vol. 12639: SPIE, pp. 483-489.

- [10] K. Ghosh, K. Hatua, and A. Mitra, "Design and Development of DSP-FPGA based Control Board for Electric Vehicle (EV) Applications," in 2022 Second International Conference on Power, Control and Computing Technologies (ICPC2T), 2022: IEEE, pp. 1-6.

- [11] L. A. Ajao, J. Agajo, B. U. Umar, T. T. Agboade, and M. A. Adegboye, "Modeling and implementation of smart home and self-control window using FPGA and Petri net," in 2020 IEEE PES/IAS PowerAfrica, 2020: IEEE, pp. 1-5.

- [12] M. Kumar, A. Jayalaxmi, and W. Malemnganbi, "Design and Implementation of Secured Car Parking System using FPGA," International Journal of Applied Engineering Research, vol. 17, no. 3, pp. 180-188, 2022.

- [13] M. H. B. Saif, N. U. Sadad, and M. N. I. Mondal, "FPGA Implementation of Educational RISC-V Processor Suitable for Embedded Applications," in 2023 International Conference on Electrical, Computer and Communication Engineering (ECCE), 2023: IEEE, pp. 1-5.

- [14] G. Surekha, G. Madesh, M. P. Kumar, and H. Sriramoju, "Design and Implementation of Arithmetic and Logic Unit (ALU)," in 2023 2nd International Conference on Applied Artificial Intelligence and Computing (ICAAIC), 2023: IEEE, pp. 1530-1536.

- [15] A. K. Panigrahi, S. Patra, M. Agrawal, and S. Satapathy, "Design and Implementation of a high speed 4bit ALU using BASYS3 FPGA Board," in 2019 Innovations in Power and Advanced Computing Technologies (i-PACT), 2019, vol. 1: IEEE, pp. 1-6.

- [16] N. Sağlam and F. Kaçar, "Design and Simulation of 64 Bit FPGA Based Arithmetic Logic Unit," Electrica, vol. 19, no. 2, pp. 158-165, 2019.

- [17] B.Karakaya, F.Çulcu and M.Türk, "Digitally Programmable Multi-Scroll Chaos Generator On FPGA" European Journal of Technique (EJT), vol.10, no.2, pp.207-216,2020.

- [18] A. Keskin and İ. Koyuncu, "Yeni Bir FPGA Geliştirme Kartı Tasarımı ve Uygulaması.", Bilgisayar Bilimleri ve Teknolojileri Dergisi, vol.3, no.2, pp.46-55, 2022.

- [19] J. Zhao, Z. Wang, and J. Chen, "Design of Pocket Development Board Based on FPGA," in IOP Conference Series: Materials Science and Engineering, 2018, vol. 382, no. 4: IOP Publishing, p. 042030.

- [20] L. Gao, "Development of FPGA experiment and development board," in World Automation Congress 2012, 2012: IEEE, pp. 1-4.

- [21] https://www.fpgadeveloper.com/list-of-fpga-dev-boards-with-wifibluetooth/ (accessed 30.11.2023).

#### **BIOGRAPHIES**

**Nebi Karagedik** graduated from Marmara University, Department of Electronic Communications Technology in 2022. He has been working as a general manager for 5 years in his own electronic R&D company headquartered in Istanbul. Smart Home Systems (KNX Bus) has been developed and offered as a product. It has developed a domestic PLC module and offered it as a product. With some of his studies in the field of reverse engineering, he developed low-cost educational FPGA boards. His current research interests include RF communication, Industrial Control Devices, FPGA and MCU based Embedded Systems.

Sezen Bal oreceived her B.Sc. degree in Electronic and Computer Department from Technical Education Faculty in Marmara University, Turkey, in 2004. She received M.Sc. and Ph.D. degree in Electronics and Computer Education from Marmara University Institute for Graduate Studies in Pure and Applied Sciences, in 2007 and 2014, respectively. She is currently working at the Department of Computer Technologies at Marmara University, Turkey. Her research interests include Remote Laboratories, Electronic Circuit Design with Embedded Systems, Computer Programming Languages.

Ayşe Yayla received her B.Sc. degree in Electronic and Computer Department from Technical Education Faculty in Marmara University, Turkey. She received M.Sc. and Ph.D. degree in Electronics and Computer Education from Marmara University Institute for Graduate Studies in Pure and Applied Sciences, in 2007 and 2018, respectively. She is an Assistant Professor in the Department of Electronics and Automation in Marmara University, Istanbul, Turkey since 2018. Her research interests include Speech Recognition, Communication Systems, Remote and Mobile Laboratories, LabVIEW, and Digital Circuit Design. She has participated 3 national projects and authored or co-authored papers in major conferences and journals.