# Reduction of Output Impedance of Buck Converter with Genetic Algorithm

Farzin Asadi

Abstract—This paper introduces a technique to reduce the output impedance in the PWM buck converters with voltage-mode control (VMC) without requiring low Equivalent Series Resistance (ESR) output capacitors. Proposed technique uses the infinity norm ( $H_{\infty}$ ) to convert the problem into an optimization problem. Obtained optimization problem is solved with the aid of Genetic Algorithm (GA). The proposed technique is applied to a sample buck converter operating in Continuous Conduction Mode (CCM). Simulink simulation is used to test the suggested method. Simulation results showed a considerable decrease in the low frequency region of output impedance. Such a decrease in output impedance is very desired for low voltage high current loads like computer CPU's.

Index Terms— DC-DC converters, load transients, output impedance of buck converter, State Space Averaging (SSA).

#### I. INTRODUCTION

MANY ATTEMPTS have been made to improve the dynamic response of PWM buck converters to a step change in load current. In [1] an averaged model of an active clamp buck converter was obtained. In this paper, output impedance of the active clamp buck converter has been modeled including the clamp capacitor effect. In [2] V2 control is used to achieve fast transient response. V2 control can take advantage of the instant feedback of the output voltage during the load transient and delay of the error amplifier is eliminated. In [3] the effects of various control techniques on the transient response of switching power supply have been discussed and compared. In this paper, transient response of switching power supply is improved by using double voltage loop control technique. In [4] the transient response of the Voltage Regulator Module (VRM) output voltage when the processor has a fast load change is analyzed. Effect of parasitic are considered in this paper. In [5] fast and efficient controller for a buck converter which supplies a microprocessor is developed and tested. Experimental data shows: tight static and dynamic regulation (± 55mV), fast transient response (within 1us), high efficiency (up to 90%), and stable operation with good noise immunity. [6] used hysteretic current-mode control in

**FARZIN ASADI**, is with the Department of Electrical Engineering, Maltepe University, Istanbul, Turkey, (e-mail: <a href="mailto:farzinasadi@maltepe.edu.tr">farzinasadi@maltepe.edu.tr</a>).

https://orcid.org/0000-0002-5928-0807

Manuscript received March 31, 2022; accepted July 18, 2022.

DOI: 10.17694/bajece.1096188

Continuous Conduction Mode (CCM) to control a Buck converter which feeds a low voltage microprocessor load. Experimental results for a 5.0 V input, 3.1V output, 13A Buck converter are included to verify the design. In [7] analytical equations are derived for a DC-DC converter at high slew-rate load current transients. The analyzed model includes synchronous buck converter, controller, output capacitor and supply bus parasitic. This paper studies the impacts of system parameters on output voltage transient response. [8] studied the role of the inductor on dynamic response of the converter and used optimization to determine the best value to obtain a fast response for loads like microprocessor. [9] presented a method to synthesis a zero-impedance converter. This method requires both a positive current feedback and a negative voltage feedback for synthesis as well as a current sensing device. [10] presented a method to achieve near optimum dynamic regulation by combining feed-forward of the output current and input voltage with current-mode control (CMC). A common method used in industry to control the output impedance is to use many output filter capacitors placed in parallel to reduce the ESR. In this approach, the feedback compensator is designed to provide the loop gain and phase margin for stability and the peak closed-loop output impedance is achieved through proper selection of low ESR output capacitors.

Feedback control is another technique to decrease the output impedance of a converter. [11] discussed the technical motivation behind compensation, derivation of analytical and design oriented transfer functions. It provides an illustrative example as well. [12] used loop shaping to design an optimum controller for a buck converter. Loop shaping method is easy and intuitive and the controller can be designed accurately for a specific phase margin and cross over frequency. [13] is a tutorial on how to design different types of classic controllers for a Buck converter. [14] presents the internal control loop operation of the BQ 2472x/3x Buck controller IC as well as the external compensator design guideline. It contains a design example based on practical specifications is demonstrated. [15-17] contains some guidelines to select the components of a second order compensation network which controls a buck converter. [18] discussed the digital PI controller design procedure for a buck converter. Experimental results showed the effectiveness of designed controller to keep the output voltage stable despite of disturbances like input voltage variations and output load changes. [19] discussed the procedure to extract the input and output impedance of dc-dc converters. Input and output impedance of buck, buck-boost and boost converters are studied there. Extraction of small

signal model is the first step for designing a linear controller for a converter. [20] discussed the procedure to extract the small signal linear model of dc-dc converters. [21] used a synchronous buck converter with Gallium Nitride (GaN) to design a driver for a laser diode. Use of GaN based switch increased the efficiency to 96.6%.

In this paper effect of parasitic elements on the operation of the converter is studied. This paper introduces a technique to reduce the output impedance in the PWM buck converters. The technique translates the reduction of output impedance into an optimization problem. Obtained optimization problem is solved with the aid of GA.

This paper is organized as follows: Dynamics of buck converter is studied in the second section. Small signal transfer functions of buck converter are extracted with the aid of State Space Averaging (SSA). Third section introduces the suggested technique. Simulink simulations are done in the fourth section. Finally, suitable conclusions are drawn.

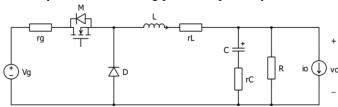

## II. DYNAMICS OF THE BUCK CONVERTER

The circuit diagram of an open-loop buck converter is shown in Fig. 1. The buck converter composed of two switches, a MOSFET switch and a diode. In this schematic, Vg, rg, L, rL, C, rC and R shows input DC source, input DC source internal resistance, inductor, inductor ESR, capacitor, capacitor ESR and load, respectively. iO is a fictitious current source added to the schematic in order to calculate the output impedance of converter. In this section we assume that converter works in CCM. MOSFET switch is controlled with the aid of a Pulse Width Modulator (PWM) controller. MOSFET switch keeps closed for D.T seconds and (1 - D).T seconds open. D and Tshow duty ratio and switching period, respectively.

Fig. 1. Schematic of a buck converter.

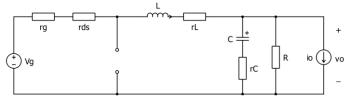

When MOSFET is closed, the diode is opened (Fig. 2).

Fig. 2. Equivalent circuit of a buck converter for closed MOSFET.

The circuit differential equations can be written as:

$$\begin{cases} \frac{di_{L}(t)}{dt} = \frac{1}{L} \left( -\left( r_{g} + r_{ds} + r_{L} + \frac{R \times r_{C}}{R + r_{C}} \right) i_{L} - \frac{R}{R + r_{C}} v_{C} + \frac{R \times r_{C}}{R + r_{C}} i_{o} + v_{g} \right) & (1) & \tilde{v}_{o} = 0.0476 \frac{(s + 6079)(s + 1846)}{s^{2} + 5799s + 2.28 \times 10^{7}} \\ \frac{dv_{C}(t)}{dt} = \frac{1}{C} \left( \frac{R}{R + r_{C}} i_{L} - \frac{1}{R + r_{C}} v_{C} - \frac{R}{R + r_{C}} i_{o} \right) & (2) & \tilde{v}_{g} = 571.43 \frac{(s + 6079)}{s^{2} + 5799s + 2.28 \times 10^{7}} \\ v_{o} = r_{C} C \frac{dv_{C}}{dt} + v_{C} = \frac{R \times r_{C}}{R + r_{C}} i_{L} + \frac{R}{R + r_{C}} v_{C} - \frac{R \times r_{C}}{R + r_{C}} i_{o} & (3) & \frac{\tilde{v}_{o}}{\tilde{d}} = 45385 \frac{(s + 6079)}{s^{2} + 5799s + 2.28 \times 10^{7}} \end{cases}$$

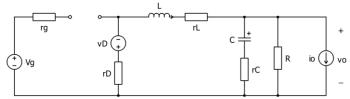

When MOSFET is opened, the diode is closed (Fig. 3).

Fig. 3. Equivalent circuit of a buck converter for opened MOSFET.

The circuit differential equations can be written as:

$$\begin{cases} \frac{di_{L}(t)}{dt} = \frac{1}{L} \left( -\left( r_{D} + r_{L} + \frac{R \times r_{C}}{R + r_{C}} \right) i_{L} - \frac{R}{R + r_{C}} v_{C} + \frac{R \times r_{C}}{R + r_{C}} i_{O} - v_{D} \right) & (4) \\ \frac{dv_{C}(t)}{dt} = \frac{1}{C} \left( \frac{R}{R + r_{C}} i_{L} - \frac{1}{R + r_{C}} v_{C} - \frac{R}{R + r_{C}} i_{O} \right) & (5) \end{cases}$$

$$v_o = r_c C \frac{dv_c}{dt} + v_c$$

$$= \frac{R \times r_c}{R + r_c} i_L + \frac{R}{R + r_c} v_c - \frac{R \times r_c}{R + r_c} i_o$$

(6)

State Space Averaging (SSA) can be used to extract the small signal transfer functions of the DC-DC converter. The procedure of state space averaging is explained in detail in [22] and [23].

The MATLAB program applies the SSA procedure to a buck converter with component values as given in Table 1. Component (the capacitor, the inductor and the load resistance) values shown in Table 1 are calculated with the aid of the procedure given in [22]. In this table, for the sake of simplicity, typical values are assumed for diode and MOSFET parameters.

TABLE I THE BUCK CONVERTER PARAMETERS

|                                      | Nominal Value          |

|--------------------------------------|------------------------|

| Output voltage, Vo                   | 1.5 V                  |

| Duty ratio, D                        | 0.156                  |

| Input DC source voltage, Vg          | 12 V                   |

| Input DC source internal resistance, | 0 Ω                    |

| rg                                   |                        |

| MOSFET Drain-Source resistance,      | 15 mΩ                  |

| rds                                  |                        |

| Capacitor, C                         | 3290 μF                |

| Capacitor ESR, rC                    | $1.4~\mathrm{m}\Omega$ |

| Inductor, L                          | 13 μΗ                  |

| Inductor ESR, rL                     | 9 mΩ                   |

| Diode voltage drop, vD               | 0.39 V                 |

| Diode forward resistance, rD         | 15 mΩ                  |

| Load resistor, R                     | 0.2-3 Ω                |

| Nominal load resistor                | 1 Ω                    |

| Switching Frequency, Fsw             | 200 kHz                |

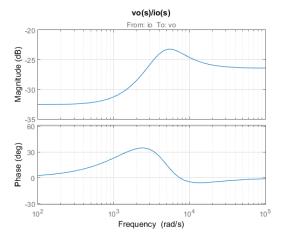

Following results are obtained after running the MATLAB

$$\frac{\tilde{v}_o}{\tilde{\iota}_o} = 0.0476 \frac{(s + 6079)(s + 1846)}{s^2 + 5799s + 2.28 \times 10^7}$$

$$\frac{\tilde{v}_o}{s} = 571.43 \frac{(s + 6079)}{s^2 + 5799s + 2.28 \times 10^7}$$

(8)

$$\frac{\tilde{v}_o}{\tilde{d}} = 45385 \frac{(s + 6079)}{s^2 + 5799s + 2.28 \times 10^7} \tag{9}$$

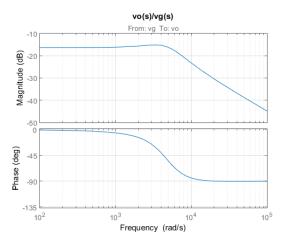

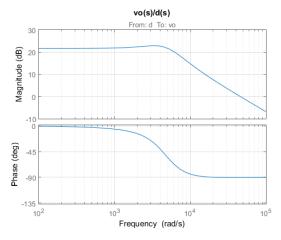

Bode diagram of these transfer functions are shown in Figs. 4, 5 and 6. All of the obtained transfer functions are stable and minimum phase since they don't have any pole or zero in the Right Half Plane (RHP). Based on the obtained results, the dynamic model shown in Fig. 7 can be suggested to the studied converter.

Fig. 4. Bode diagram of  $\frac{\tilde{v}_o}{\tilde{\iota}_o} = 0.0476 \frac{(s+6079)(s+1846)}{s^2+5799s+2.28\times10^7}$

Fig. 5. Bode diagram of  $\frac{\tilde{v}_o}{\tilde{v}_g} = 571.43 \frac{(s+6079)}{s^2+5799s+2.28\times10^7}$

Fig. 6. Bode diagram of  $\frac{\tilde{v}_o}{d} = 45385 \frac{(s+6079)}{s^2+5799s+2.28\times10^{7}}$

Fig. 7. Dynamical model of the studied buck converter.

## III. SUGGESTED METHOD

This section introduces the suggested method. Infinity norm and genetic algorithm make the foundations of the proposed method and are studied briefly.

# A. $H_{\infty}$ Norm

The steady-state output of the SISO stable system,

$$\dot{x} = Ax + Bu

y = Cx$$

(10)

to the input function,

$$u(t) = a\sin(\omega t + \varphi) \tag{11}$$

with unknown  $a \neq 0$ ,  $\omega$ ,  $\varphi \in \mathbb{R}^1$  is

$$y_{ss}(t) = |G(j\omega)|. a. \sin(\omega t + \varphi + arg(G(j\omega)))$$

(12)

where  $G(s) = C(sI - A)^{-1}B$ . The  $H_{\infty}$ -norm is the maximal possible amplification, i.e.

$$||G(.)||_{\infty} = \frac{\sup |G(s).U(s)|}{\sup |U(s)|} = \frac{\sup |G(j\omega)|}{\omega \in \mathbb{R}^{1}}$$

$$(13)$$

$\omega \in \mathbb{R}^1$  The  $H_{\infty}$ -norm of a MIMO system is its maximum singular value [24].

$$||G(.)||_{\infty} = \sup_{\omega} \bar{\sigma} \{G(j\omega)\}$$

(14)

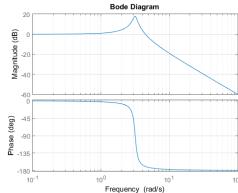

The  $H_{\infty}$ -norm of a scalar transfer function can be obtained graphically. Infinity norm of a SISO system G is the distance in the complex plane from the origin to the farthest point on the Nyquist plot of G, and it also appears as the peak value on the Bode magnitude plot of  $|G(j\omega)|$ . For instance, the infinity norm of  $G(s) = \frac{10}{s+0.4s+10}$  is 7.91. Bode plot of  $G(s) = \frac{10}{s+0.4s+10}$  is shown in Fig. 8. Maximum of the Bode graph occurs around 42  $\frac{Rad}{s}$  and its value is 17.96 dB which is equivalent to gain of  $10^{\frac{17.96}{20}} = 7.91$ .

Fig. 8. Bode plot of  $G(s) = \frac{10}{s + 0.4s + 10}$ . Peak occurs at 3.15 Rad/s with magnitude of 17.96 dB.

## B. Genetic Algorithm (GA)

In 1960 the first serious investigation into Genetic Algorithm (GA) was undertaken by John Holland. These search techniques are based on the process of biological evolution and are used to provide useful solutions to optimization and search problems. As they are based on biological evolution, they use techniques that are emulated from the concepts of inheritance, mutation and selection.

Genetic algorithms explore a parameter space while optimizing a function. The problem is broken down into a *population* of candidate solutions which are refined over a number of *generations*.

A single candidate solution is represented by a *chromosome* which essentially encodes all of the optimizable parameters into a single entity. Each candidate is ranked using a fitness function and those with the best fitness score are selected for further refinement. The refinement stage then operates on each of the chromosomes by

I) *breeding* - a process where a new population of improved candidates are generated using the present generation's population, and

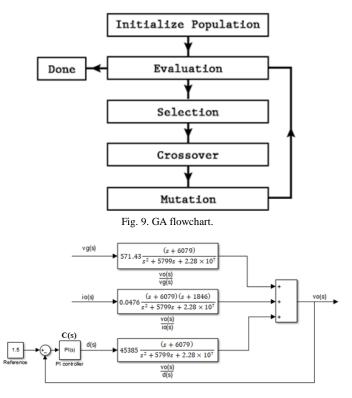

II) *mutation* - in which chromosomes are modified in some way. Both of these operations permit the parameter space to be more effectively explored. The whole process is iterated for many generations where the candidate solutions can be seen to evolve and, hopefully, converge towards a single solution. The use of natural evolution method for the optimization of control system has been of interest for the researchers since a long time. Fig. 9, illustrate the GA flowchart.

Ready to use implementation of GA is available in the MATLAB's optimization toolbox.

Fig. 10. Block diagram of the system with PI controller.

## C. Suggested Method

The open loop dynamical model of the studied buck converter is shown in Fig. 7. Block diagram of closed loop voltage mode control of the converter is shown in Fig. 10. The controller is PI (Proportional Integral) since it is good enough for most of applications.

The PI controller must stabilize the loop. According to the Routh-Hurwitz stability test, following inequality must be satisfied in order to stabilize the loop.

$$(a.d + b.c)k_p + (a.c - b)k_i + c.d + a^2.k_p k_i + a.b.k_p^2 > 0$$

(15) where,  $a = 45385$ ,  $b = 45385 \times 6079 = 275895415$ ,  $c = 5799$ ,  $d = 2.28 \times 10^7$ .  $k_p > 0$  and  $k_i > 0$  are unknown proportional gain and integral gain, respectively.

According to the Fig. 10, the closed loop output impedance is:

$$Z_{CL} = \frac{\tilde{v}_o(s)}{\tilde{\iota}_o(s)} \times \frac{1}{1 + C(s) \cdot \frac{\tilde{v}_o(s)}{\tilde{d}(s)}}$$

(16)

or,  $Z_{CL}$   $= 0.0476 \frac{(s + 6079)(s + 1846)}{s^2 + 5799s + 2.28 \times 10^7} \times \frac{1}{1 + (k_p + \frac{k_i}{s}).45385 \frac{(s + 6079)}{s^2 + 5799s + 2.28 \times 10^7}}$ (17)

Equation (17) has two unknowns:  $k_p$  and  $k_i$ . We want to solve the following optimization problem:

$$\min \|Z_{CL}\|_{\infty}$$

$$s.t.C(s) \ stabilize \ \frac{\tilde{v}_o(s)}{\tilde{d}(s)}$$

(18)

Ideally  $Z_{CL}$  would be zero across the frequency bandwidth. However, since that would require an infinite loop gain, it is not practical for synthesis. The GA can be used to solve this optimization problem. GA changes the  $k_p$  and  $k_i$  values until the minimum is obtained. After running the GA,  $k_p = 3.733$  and  $k_i = 1.108 \times 10^4$  and min  $\|Z_{CL}\|_{\infty} = 0.476 \ \Omega$ .

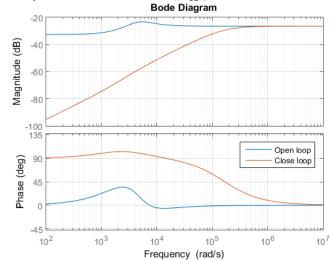

Fig. 11. Comparison between open loop output impedance and closed loop output impedance.

Fig. 11 compares the closed loop output impedance (Equation (17) with  $k_p = 3.733$  and  $k_i = 1.108 \times 10^4$ ) and open loop output impedance (Equation (7)). Closed loop output impedance decreased considerably in the low frequency range of the graph. Reduction of output impedance means a smaller voltage drop for larger currents. Such a property is highly desired in low voltage high current applications.

#### IV. SIMULATION RESULTS

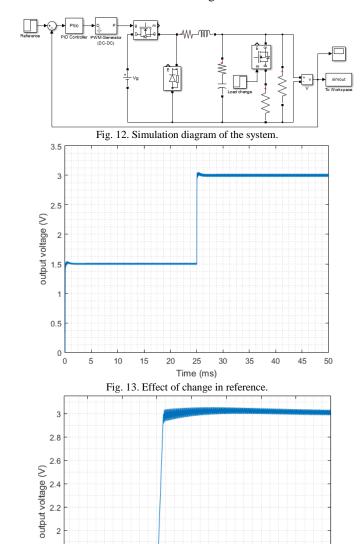

Designed PI controller is tested in the Simulink environment. Simulation diagram is shown in Fig. 12. In the first test scenario, reference (Fig. 10) changes from 1.5 V to 3 V at t= 25 ms. Simulation result is shown in Figs. 13 and 14. Simulation result shows that the designed controller is able to follow the reference signal with zero steady state error. This is expected since the controller contains an integrator term.

Fig. 14. Close-up Fig. 13 around t= 25 ms.

25.2 Time (ms)

1.8

24.6

24.8

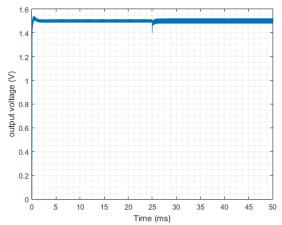

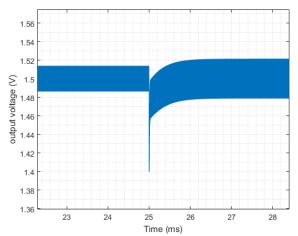

In the second scenario load current changes from 0.5 A to 5 A at t=25 ms. Simulation result is shown in Figs. 15 and 16. Simulation result shows that the controller is able to keep tracking the reference voltage even when the load changes. According to Fig. 16, maximum deviation for change of output current from 0.5 A to 5 A is 1.5-1.4=0.1 V. In other words, change of 900% in output current generates change of 6.66% in output voltage. Such a small change in output voltage shows that the designed controller decreased the output impedance considerably.

Fig. 15. Effect of change in output load.

Fig. 16. Close-up Fig. 15 around t= 25 ms.

## V. CONCLUSIONS

A technique to reduce the output impedance in the PWM buck converters with voltage-mode control is studied in this paper. Proposed technique used the  $H_{\infty}$  infinity norm to convert the impedance reduction problem into an optimization problem and use genetic algorithm to solve the obtained optimization problem. Suggested technique is cheaper in comparison to the classical solution of using the capacitors with lower ESR. Because in the suggested technique, there is no need to use any expensive low ESR capacitor and reduction of output impedance is done by good selection of controller parameters. Suggested technique is tested with the aid of Simulink simulations. According to the simulation results, the output impedance of converter decreased considerably in the low frequency region. Such a decrease is very desired for low

voltage high current loads like computer CPU's. Suggested method can be applied to other types of converters as well.

#### REFERENCES

- E. Joard, J. Villarejo, F. Soto, and J. Muro, "Effect of the Output Impedance in Multiphase Active Clamp Buck Converters," IEEE Trans. Ind. Electron., vol. 55, no. 9, pp. 3231-3238, Sep. 2008.

- [2] D. Goder and W. R. Pelletier, "V2 architecture provides ultra-fast transient response in switch mode power supplies," in Proc. HFPC, 1996, pp. 16-23.

- [3] J. Xu, X. Cao, and Q. Luo, "The effects of control techniques on the transient response of switching DC-DC converters," in Proc. IEEE PEDS, 1999, pp. 794-796

- [4] P. Wong, F. C. Lee, X. Zhou, and J. Chen, "VRM transient study and output filter design for future processors," in Proc. IEEE IECON, 1998, pp. 410-415.

- [5] D. Briggs, R. Martinez, R. Miftakhutdinov, and D. Skelton, "A fast, efficient synchronous buck controller for microprocessor power supplies," in Proc. HFPC, 1998, pp. 170-176.

- [6] B. Arbetter and D. Maksimovic, "DC-DC converter with fast transient response and high efficiency for low-voltage microprocessor loads," in Proc. IEEE APEC, 1998, pp. 156-162.

- [7] R. Miftakhutdinov, "Analysis of synchronous buck converter with hysteretic controller at high slew-rate load current transients," in Proc. HPFC, 1999, pp. 55-69.

- [8] C. J. Mehas, K. D. Coonley, and C. R. Sullivan, "Converter and inductor design for fast response microprocessor power delivery," in Proc. IEEE PESC, 2000, pp. 1621-1626.

- [9] L. D. Varga and N. A. Losic, "Synthesis of zero-impedance converter," IEEE Trans. on Power Electronics, vol. 7, no. 1, Jan 1992.

- [10] R. Redl and N. Sokal, "Near-optimum dynamic regulation of dc-dc converters using feed forward of output current and input voltage with current-mode control," IEEE Trans. on Power Electronics, vol. PE-1, no. 3. Jul 1986

- [11] J. Steenis, "Details on compensating voltage mode buck regulators," Power Management Design Line, September 4, 2006.

- [12] W.H. Lei, T.K. Man, "A general approach for optimizing dynamic response for buck converter," ON Semiconductor, Apr. 2004.

- [13] T. Hagerty, "Voltage-mode control and compensation: Intricacies for buck regulators," Electronics Design, Strategy, News (edn.com), June 30, 2008.

- [14] L. Zhao, "Closed-loop compensation design of a synchronous switching charger using bq2472x/3x," Texas Instruments application report, September 2006.

- [15] "A handy method to obtain satisfactory response of buck converter," Analog Integrations Corporation, application note AN021, October 2001.

- [16] "Loop compensation of voltage-mode buck converters," Sipex Corporation Technical Note, October 11, 2006.

- [17] D. Mattingly, "Designing stable compensation networks for single phase voltage mode buck regulators," Intersil Corporation Technical Note TB417.1, December 2003.

- [18] H. Sucu, T. Goktas, M. Arkan, "Design, simulation and application of buck converter with digital PI converter", Balkan Journal of Electrical and Computer Engineering, April 2021.

- [19] F. Asadi, K. Eguchi, "On the Extraction of Input and Output Impedance of PWM DC-DC Converters", Balkan Journal of Electrical and Computer Engineering, April 2019.

- [20] F. Asadi, "On the Extraction of Input and Output Impedance of PWM DC-DC Converters", Balkan Journal of Electrical and Computer Engineering, April 2019.

- [21] H. Sucu, T. Goktaş M. Arkan, "A GaN-Based Synchronous Buck Converter for High Power Laser Diode Drive Applications", Balkan Journal of Electrical and Computer Engineering, Nisan 2021.

- [22] Asadi F, Eguchi K. Dynamics and control of DC-DC converters, San Rafael: Morgan and Claypool; 2018. p. 89-145.

- [23] Suntio T. Dynamic profile of switched mode converter: modeling, analysis and control. New Jersy: John Wiley & Sons. 2009. p. 17-37.

- [24] Gu D, Petkov P, Konstantinov M. Robust Control Design with MATLAB.Springer. 2013. p. 9-11.

## **BIOGRAPHY**

FARZIN ASADI received his B.Sc. in Electronics Engineering, M.Sc. in Control Engineering, and Ph.D. in Mechatronics Engineering. Currently, he is with the Department of Electrical and Electronics Engineering at Maltepe University, Istanbul, Turkey.

Dr. Asadi has published more than 40 international papers and 15 books. He is on the editorial board of 7 scientific journals as well. His research interests include switching converters, control theory, robust control of power electronics converters, and robotics.